## SH-2015

## ACADEMIC BOOK

### **SEMESRTER VII**

BE-ELECTRONICS SH-2015

### ACADEMIC BOOK

### <u>INDEX</u>

| SR.<br>NO. | CONTENT                          | PAGE NO. |

|------------|----------------------------------|----------|

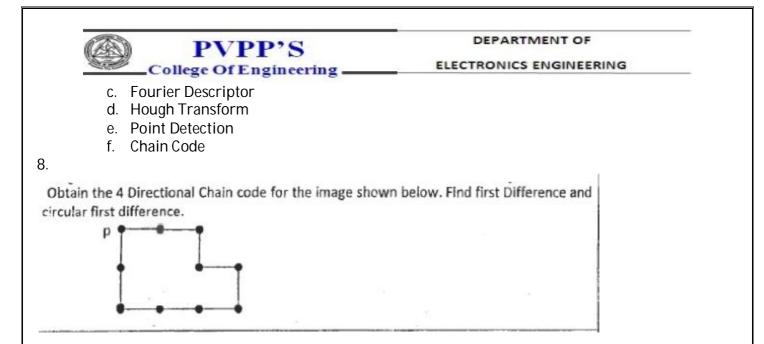

| 1          | Rules & Regulation               | 03       |

| 2          | Academic calender                | 04       |

| 3          | Digital Image Processing         | 07       |

| 4          | IC Technology                    | 40       |

| 5          | Embedded Systems Design          | 54       |

| 6          | Computer Communication & Network | 74       |

| 7          | Power Electronics-II             | 90       |

### **Rules and Regulations**

### College Timings:

The college timing is from 8:45 AM to 4:45 PM .The students must follow the college timing.

### Academic calendar and Time table:

The details of academic curriculum and activities are mentioned in the academic book. The students are required to strictly follow the class Time table and academic calendar.

### Attendance:

All students are hereby informed that attendance for lectures/practical/tutorials is compulsory. Mumbai University does not allow students to appear for examination if their attendance is less than 75%. But for the good academic performance of the students, the department expects 100 % attendance in theory and practical separately.

### Defaulters:

Defaulters list will be displayed monthly. The defaulter students are required to bring their parents/guardians within four days after the display of defaulters list. If students remain defaulter consistently he/she has to face the consequences as laid by the Mumbai University.

### Identity card:

Student must wear ID during college hours in the campus.

### Mobile Phone:

Use of cell phone is strictly prohibited in the college premises.

### **Examination:**

As per the university norms, there will be two term test i.e Mid Term test and End Term test in the semester which is an integral part of Internal Assessment for every subject. Both the examination will be based on 40 % and 70 % of theory syllabus respectively for each subject and will be conducted as per the dates mentioned in the academic calendar. Attendance for both internal examination IS COMPULSORY .As per the university norms, no retest will be conducted under any circumstances. Separate passing heads is compulsory for internal and external examination for individual subjects. If the student fails in any of the exam he/she has to reappear in the concerned subject after the declaration of the result.

### Practicals/tutorials/Assignments:

The Student should compulsory bring their rough and fair journal for the concerned subject for every practical and tutorials and get it checked regularly. Failing to do so, they will not be allowed for the practical. The Assignments for every subject should be submitted on regular basis. The student must abide by the above mentioned rules and regulations laid down by the department for their better and brighter future.

DEPARTMENT OF

College Of Engineering \_\_\_\_\_ ELECTRONICS ENGINEERING

### ACADEMIC CALENDER SH-2015

### COMMENCEMENT OF SEMESTER

| Sr. No. | Date                                                            | Activity                                                                                                                                                                                                                                                                                                                       | Responsibility                                                                                         |

|---------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 1       | June 06, 2015                                                   | Mini Project Orientation Seminar for TE                                                                                                                                                                                                                                                                                        | TE Project Coordinators                                                                                |

|         | June 30, 2015                                                   | Display of Timetable                                                                                                                                                                                                                                                                                                           | Time Table Committee                                                                                   |

| 2       | July14, 2015                                                    | Commencement of Term<br>Address of HODs/ faculty to the student with faculty introduction. Theory and<br>lab period as per time table. (Small orientation lecture are to be organized<br>on first day and course content with industry relevance to be illustrated for<br>all classes. Rules regulations to be explained too.) | HODs / CAs and faculties<br>Distribution of Academic Book to all students<br>Semester wise I.III,V,VII |

| 3       | July 18, 2015                                                   | Ramzan-Id                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| 4       | July 24, 2015                                                   | Final Mini Project Group Formation(TE)                                                                                                                                                                                                                                                                                         | TE Project Coordinator                                                                                 |

| 5       | July 24, 2015                                                   | Project approval seminar and Display of approved project : Title and Name of<br>Guide                                                                                                                                                                                                                                          | BE Project coordinator                                                                                 |

| 6       | As per department's academic Calendar                           | Lecture Series                                                                                                                                                                                                                                                                                                                 | As per departmental Academic Time Table                                                                |

| 7       | July 31, 2015                                                   | Project Approval Seminar (TE)                                                                                                                                                                                                                                                                                                  | Project coordinator                                                                                    |

| 9       | August 06, 2015                                                 | Display of approved Mini project(TE)                                                                                                                                                                                                                                                                                           | TE Project Coordinator                                                                                 |

| 10      | August 11-14, 2015                                              | Introduction & Initial Mini Project development (TE)                                                                                                                                                                                                                                                                           | TE Project Coordinator                                                                                 |

| 11      | August 14, 2015                                                 | Display of defaulter's list – I                                                                                                                                                                                                                                                                                                | Class Advisors/HODs<br>(Reports to be generated through MIS)                                           |

| 12      | August 14,2015                                                  | Fresher's Party                                                                                                                                                                                                                                                                                                                | Student's Council & SE Students                                                                        |

| 13      | August 15,2015                                                  | Independence Day                                                                                                                                                                                                                                                                                                               | Celebrated in the college as per circular                                                              |

| 14      | August 17-21, 2015                                              | Literature Survey                                                                                                                                                                                                                                                                                                              | TE Project Coordinator                                                                                 |

| 15      | August 18,2015                                                  | Parsi New Year                                                                                                                                                                                                                                                                                                                 |                                                                                                        |

| 16      | August 17 <sup>m</sup> ,18 <sup>m</sup> & 19 <sup>m</sup> ,2015 | Students Feedback 1                                                                                                                                                                                                                                                                                                            | Sys Admin<br>(Online feedback in coordination with the<br>departments)                                 |

| 17      | August 24-26,2015                                               | Mid Term Test                                                                                                                                                                                                                                                                                                                  | HODs, CAs                                                                                              |

#### DEPARTMENT OF

### College Of Engineering \_\_\_\_\_ ELECTRONICS ENGINEERING

| 18 |                           | BE Project Review – I                                        | BE Project coordinator                                             |

|----|---------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|

| 19 | August Last week 2015     | Mini Project Review                                          | TE Project Coordinator                                             |

| 20 | September 1-4, 2015       | Practical work of Mini Project activities                    | TE Project Coordinator                                             |

| 21 | September 6,2015          | Gopakala                                                     |                                                                    |

| 22 | September7 to 11th ,2015  | Parent Teachers Interaction Meeting                          | HODs/ CAs                                                          |

| 23 | September 8-18, 2015      | Implementation of Mini Project                               | TE Project Coordinator                                             |

| 24 | September 14 , 2014       | Display of defaulter's list – 2                              | Class Advisors/ HODs<br>(Reports to be generated through MIS)      |

| 25 | September 14 to 18th,2015 | On line Examination                                          | Coordinators/SysAdministrator/Subject<br>Teacher                   |

| 26 | September 15, 2015        | Felicitation to toppers (Engineers Day)                      | Principal and Student's Council                                    |

| 27 | September 17, 2015        | Shri Ganesh Sthacana                                         | Principal and Student's Council                                    |

| 28 | September 18, 2015        | Project Review – II and Submission of softcopy of synopsis   | BE Project coordinator                                             |

| 29 | September 21,2015         | ShriGanesh Visarian                                          | Principal and Student's Council                                    |

| 30 | September 22-25, 2015     | Results & Conclusion                                         | TE Project Coordinator                                             |

| 31 | September 25 ,2015        | Bakari ID (ID UL ZUHA)                                       |                                                                    |

| 32 | September 27,2015         | Anant Shatwdashi                                             |                                                                    |

| 33 | September 28-30 , 2015    | Students Feedback 2                                          | Sys Admin<br>(Online feedback in coordination with<br>departments) |

| 34 | September Last week       | Mini Project review-II                                       | TE Project Coordinator                                             |

| 35 | October 2,2015            | Mahatma Gandhi Jayanti                                       |                                                                    |

| 36 | October 5-7,2015          | End Term Test                                                | HODs, CAs                                                          |

| 37 | October 09, 2015          | Final certification and submission of synopisis              | BE Project coordinator                                             |

| 38 | October 06, 2015          | Project Diary & Final report submitted to guide for approval | TE Project Coordinator                                             |

| 39 | October 10, 2015          | Final submission duly approved by guide                      | TE Project Coordinator                                             |

| 40 | October 12,2015           | Third Defaulter List                                         | Class Advisors/ HODs<br>(Reports to be generated through MIS       |

| 41 | October 12-23,2015        | Remedial Classes                                             | Coordinators with HODs<br>(For weaker students)                    |

| - ( | PVP                                                                                                                                                                                   | P'S DEPA                                                                    | RTMENT OF                                        |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

|     | College Of En                                                                                                                                                                         | ngineering ELECTRONI                                                        | ng ELECTRONICS ENGINEERING                       |  |  |  |

| 2   | October 22,2015                                                                                                                                                                       | Dasara                                                                      |                                                  |  |  |  |

| 3   | October 19-23 ,2015                                                                                                                                                                   | Final Certification and submission                                          | HOD<br>(As per University schedule)              |  |  |  |

| 4   | October 24,2015                                                                                                                                                                       | Moharam                                                                     |                                                  |  |  |  |

| 5   | October 26,2015                                                                                                                                                                       | Final defaulter list                                                        | HODs                                             |  |  |  |

| 6   | October 26,2015                                                                                                                                                                       | Term End                                                                    | HODs (As per University Schedule)                |  |  |  |

| 7   | October 26 to November 7,2015                                                                                                                                                         | Conduction of Oral and Practical Examinations                               | Faculties (As per University Schedule)           |  |  |  |

| 8   | November 11,2015                                                                                                                                                                      | Laxmi Puian                                                                 |                                                  |  |  |  |

| 9   | November 12, 2015                                                                                                                                                                     | Balipratiprada                                                              |                                                  |  |  |  |

| 0   | After Term End                                                                                                                                                                        | Vacation for faculties 1st Slot                                             | Exam In - Charge (As per University<br>Schedule) |  |  |  |

| 1   | November 25, 2015                                                                                                                                                                     | Gurunanak Jayanti                                                           |                                                  |  |  |  |

| 2   | 18th Nov.2015 to 19th Dec. 2015                                                                                                                                                       | Non Vacation Slot                                                           | (As per University schedule)                     |  |  |  |

| 3   | 18th November,2015 onwards                                                                                                                                                            | University Theory Examination for all Semesters                             | Exam In-Charge<br>(As per University schedule)   |  |  |  |

| 4   | 20th December-3rd Jan. 2016                                                                                                                                                           | Vacation for faculties 2 <sup>nd</sup> Slot                                 | Exam In – Charge (As per University<br>Schedule) |  |  |  |

| 5   | 24 <sup>th</sup> December,2015                                                                                                                                                        | ID-E-MILAD                                                                  |                                                  |  |  |  |

| 6   | 25 <sup>th</sup> December,2015                                                                                                                                                        | CHRISTMAS                                                                   |                                                  |  |  |  |

| 7   | January 04,2016                                                                                                                                                                       | Commencement of FH-2016                                                     |                                                  |  |  |  |

| Sun | 1) Total Working Weeks<br>2) Total Working days<br>( <u>excluding</u> Saturdays, Sundays & exa<br>3) Total Working Days for teaching<br>4) Available Periods for teaching<br>5) Tests | : 15<br>imination) : 86<br>: 73<br>:<br>Herweek (2)<br>3 42<br>4 56<br>5 70 |                                                  |  |  |  |

Note:

- a. Attendance is compulsory from first day onwards

- b. Those students who will remain absent on first day of academic semester, are compulsorily required to bring letter along with parents and meet the Principal/HOD for permission to attend the college.

02 Written test

01

c. In case of absence (even for a day or hour), students are required to submit letters from parents at the time of attending the college.

Dr. Raiendra R. Sawant Principal

# SH-2015

### DIGITAL IMAGE PROCESSING

Mrs.PRITI TYAGI PVPP COLLEGE OF ENGINEERING (ELECTRONICS ENGINEERING)

DEPARTMENT OF

ELECTRONICS ENGINEERING

### Subject Plan

**GROUP NAME: SIGNALS AND SYSTEM**

COURSE TITLE : Digital Image Processing

**COURSE CODE : EXC 7051**

SEM : VII(SH 2015)

PRE-REQUISITE : EXS 401: Applied Mathematics IV EXC 504: Signals and System

### **COURSE OBJECTIVES :**

- 1. To develop an overview of the field of image processing

- 2. To learn the fundamental concepts of Digital Image Processing.

- 3. To improve pictorial information for human interpretation and process scene data for storage, transmission and representation for autonomous machine perception.

- 4. To understand basic image enhancement and segmentation techniques.

- 5. To illustrate Image Transform calculations mathematically and develop fast transform algorithm

- 6. To learn Image Compression and Decompression Techniques

### COURSE OUTCOME :

### After successful completion of the course student will be able to

- 1. Understand the concept of Digital Image processing.

- 2. Explain image enhancement and Segmentation technique.

- 3. Understand Digital Image compression and decompression techniques

- 4. Perform Binary Image Processing Operations

ELECTRONICS ENGINEERING

### **LEARNING RESOURCES: -**

#### **RECOMMENDED BOOKS:-**

- 1. Gonzalez & Woods, Digital Image Processing, Pearson Education, Second edition.

- 2. S. Jayaraman Digital Image Processing TMH (McGraw Hill) publication

- 3. A.K. Jain, Fundamentals of Image processing, Prentice Hall of India Publication, Third Edition

#### **Reference Books:**

- 1. Mc Andrew , Introduction to Digital Image processing with Matlab, Cengage learning publication

- 2. Gonzalez & Woods, Digital Image Processing using MATLAB, Pearson Education

- 3. W. Pratt, Digital Image Processing, Wiley Publication, third edition, 2002.

### COURSE MATERIALS MADE AVAILABLE

- 1. Course instructional objectives & outcomes

- 2. Syllabus

- 3. Chapterwise Question Bank

#### **Evaluation**:

| Theory Exam                                                           | 80 M  |

|-----------------------------------------------------------------------|-------|

| Internal assessment: The average marks of Mid-term test (20 M) & End- | 20 M  |

| term test (20 M) will be considered as final IA marks                 |       |

| Oral                                                                  | 25 M  |

| Term Work                                                             | 25 M  |

| Total                                                                 | 150 M |

ELECTRONICS ENGINEERING

### List of Experiments

### Topic-1 : Image Enhancement in Spatial Domain[ Any two Experiments ]

- 1. To enhance image using Histogram Equalization

- 2. To enhance image using Point Processing Operations

- 3. To enhance image using spatial filtering

- 4. To perform Colour Image Enhancement

- 5. Removal of Salt and Pepper noise

### Topic-2 : Image Enhancement in Frequency Domain [Any One]

- 1. Find Magnitude Response and Phase Response of two images. Interchange the phase response of the two images and take Inverse Transform.

- 2. High Pass Filtering and Low pass Filtering

### Topic-3 : Image Segmentation [ Any two Experiments ]

- 1. To find edges using LOG

- 2. To find Edges using Prewit/ Sobel / Robert operators.

- 3. To find edges using canny Edge Detection.

### Topic-4 : Image Compression [ Any Two Experiments ]

- 1. To compress using Huffman coding

- 2. To compress DCT coefficient of Image

- 3. To compress Wavelet Coefficient of Image.

- 4. To compress Binary Image using Run Length Coding

### Topic-5 : Image Transform [Any two Experiments ]

- 1. Convolution Property of DFT

- 2. DWT and IDWT

- 3. Compute and plot DCT Basis

### Topic-6 : Morphological Operations [Any One]

- 1. Dilation and Erosion

- 2. Opening and Closing Operation

DEPARTMENT OF

\_College Of Engineering \_\_\_\_\_ ELECTRONICS ENGINEERING

### SYLLABUS

| Module<br>No. | Unit<br>No.                             | Topics                                                                                                                                                                                                                                                   | Hrs.  |  |  |  |

|---------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| 1             |                                         | Digital Image Processing Fundamentals                                                                                                                                                                                                                    | 06    |  |  |  |

|               | 1.1                                     | Introduction: Background, Digital Image Representation, Fundamental Steps in<br>Image Processing, Elements of a Digital Image Processing System                                                                                                          |       |  |  |  |

|               | 1.2                                     | Digital Image Fundamentals: Elements of Visual Perception, A Simple Image<br>Model, Sampling and Quantization, Some Basic Relationships between Pixels,<br>Imagining Geometry. Image File Formats : BMP, TIFF and JPEG. Colour Models<br>(RGB, HSI, YUV) |       |  |  |  |

| 2             |                                         | Image Enhancement                                                                                                                                                                                                                                        | 08    |  |  |  |

|               | 2.1                                     | Spatial Domain Methods, Frequency Domain Methods, Some Simple Intensity<br>Transformations, Histogram Processing, Image Subtraction, Image Averaging,<br>Background                                                                                      | 10.00 |  |  |  |

|               | 2.2                                     | Smoothing Filters, Sharpening Filters, Lowpass Filtering, Highpass Filtering,<br>Generation of Spatial Masks from Frequency Domain Specifications. Homomorphic<br>Filtering.                                                                             |       |  |  |  |

| 3             | 3 Image Segmentation and Representation |                                                                                                                                                                                                                                                          |       |  |  |  |

|               | 3.1                                     | Detection of Discontinuities, Edge Linking using Hough Transform, Thresholding,<br>Region based Segmentation, Split and Merge Technique,                                                                                                                 |       |  |  |  |

|               | 3.2                                     | Image Representation and Description, Chain Code, Polygonal, Representation,<br>Shape Number, Moments.                                                                                                                                                   |       |  |  |  |

| 4             |                                         | Binary Image Processing                                                                                                                                                                                                                                  | 06    |  |  |  |

|               | 4.1                                     | Binary Morphological Operators, Hit-or-Miss Transformation, Boundary Extraction,<br>Region Filling, Thinning and Thickening, Connected Component Labeling, Iterative<br>Algorithm and Classical Algorithm                                                |       |  |  |  |

| 5             |                                         | Image Transform                                                                                                                                                                                                                                          | 12    |  |  |  |

|               | 5.1                                     | Introduction to the Fourier Transform, The Discrete Fourier Transform, Some<br>Properties of the Two-Dimensional Fourier Transform Fast Fourier<br>Transform(FFT),                                                                                       |       |  |  |  |

|               | 5.2                                     | Discrete Hadamard Transform(DHT), Fast Hadamard Transform(FHT), Discrete<br>Cosine Transform(DCT), Discrete Wavelet Transform(DWT),                                                                                                                      |       |  |  |  |

| 6             |                                         | Image Compression:                                                                                                                                                                                                                                       | 12    |  |  |  |

|               |                                         | Fundamentals - Coding Redundancy, Interpixel Redundancy, Psychovisual Redundancy, Fidelity Criteria.                                                                                                                                                     |       |  |  |  |

|               | 6.1                                     | Image Compression Models – The Source Encoder and Decoder, Lossless<br>Compression Techniques : Run Length Coding, Arithmetic Coding, Huffman<br>Coding, Differential PCM,                                                                               |       |  |  |  |

|               | 6.2                                     | Lossy Compression Techniques: Improved Gray Scale Quantization, Vector<br>Quantization, JPEG, MPEG-1.                                                                                                                                                    |       |  |  |  |

|               |                                         | Total                                                                                                                                                                                                                                                    | 52    |  |  |  |

PVPP'S College Of Engineering DEPARTMENT OF

ELECTRONICS ENGINEERING

### Chapterwise Plan

Subject Title: Digital Image Processing

Chapter No. : 1

**Chapter Name : Digital Image Fundamentals**

Approximate Time Needed : 06 hrs

#### Lesson Schedule :

| em                          |

|-----------------------------|

| at at law                   |

| entation                    |

| m Sampling and Quantization |

| en pixels                   |

|                             |

|                             |

|                             |

### **Objectives:**

- 1. To define scope of Image Processing.

- 2. To give an idea of the state of the art in image processing by examining some of the principal areas in which it is applied.

- 3. To discuss principal approaches used in digital Image Processing.

- 4. To provide an overview of the image processing system which includes various elements such as Image acquisition, sampling, Quantization, Processing Storage and display

- 5. To generate digital image from sensed data.

- 6. Digital Image fundamentals

- 7. To represent image in matrix form.

- 8. To understand different image file formats.

| 1                            | PVPP'S                                                                                                                                                                                                                          | DEPARTMENT OF           |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 8                            | College Of Engineering                                                                                                                                                                                                          | ELECTRONICS ENGINEERING |

|                              |                                                                                                                                                                                                                                 |                         |

|                              | Model Questions:                                                                                                                                                                                                                |                         |

| 1. E                         | xplain the elements of digital image processing syste                                                                                                                                                                           | em. (10)                |

| (<br>r                       | te <b>true</b> or <b>false</b> and justify :<br>a) In general, fine sampling is preferred in smoo<br>egions, where grey level transitions are sharp.<br>b) Quality of the picture depends on the numl<br>represent the picture. |                         |

| (a) (<br>(b)<br>(c)  <br>(d) | Vrite short notes on the following :<br>Connectivity of pixels.<br>Image Sampling and Quantization<br>Non uniform sampling and Quantization<br>Spatial and Tonal Resolution<br>Image Acquisition Methods                        |                         |

|                              | Consider the image segment shown below:<br>3 1 2 1 (q)<br>2 2 0 2<br>1 2 1 1<br>(p) 1 0 1 2<br>Compute the length of the shortest 4, 8, and m par                                                                               | th between p & q.       |

| <b>5</b> . [                 | Define<br>a. Euclidean Distance<br>b. City Block distance<br>c. Chess Board Distance<br>d. 4, 8. M connectivity                                                                                                                 |                         |

|                              |                                                                                                                                                                                                                                 |                         |

|         | PVP<br>College Of E             | P'S<br>ngineering | ELECTRONICS ENGINEERING |  |

|---------|---------------------------------|-------------------|-------------------------|--|

|         |                                 | Chapterv          | wise Plan               |  |

| Subject | Title: Digital Im               | age Processing    |                         |  |

| Chapter | No. : 2 A                       |                   |                         |  |

|         | Name : Image                    | Enhancement in Sp | oatial Domain           |  |

|         | mate Time Nee                   | ded : 04 hrs      |                         |  |

|         |                                 | ded : 04 hrs      | er hour                 |  |

|         | Schedule :                      |                   |                         |  |

|         | Schedule :<br>Lecture No.       | Portion covered p | g operations            |  |

|         | Schedule :<br>Lecture No.<br>07 | Portion covered p | g operations<br>essing  |  |

### **Objectives:**

- 1. To yield a better quality image for the purpose of some particular application that can be done by suppressing the noise and improve the image contrast

- 2. To learn Image Enhancement algorithms employed to emphasize, sharpen or smoothen image features in spatial domain for display and analysis.

- 3. To improve the quality of an image as perceived by a human being.

- 4. To discuss a number of techniques for intensity transformations and spatial filtering

### Model Questions:

..State true or false and justify (4 marks each)

(a) Enhancement process does not change the information contents of the image.

(b) For digital images having salt-pepper noise, median filter is the best filter.

(c) The discrete histogram equalization technique will not, in general, yield a flat histogram.

(d) A Highpass - filtered image can be obtained in the spatial domain as

Highpass = Original - Lowpass.

(e) The principal operation of median filter is to force points with distinct intensities to be more like their neighbors.

DEPARTMENT OF

College Of Engineering

ELECTRONICS ENGINEERING

(f) Second pass of Histogram equalization will produce same result as the first pass.

(g) The sum of the coefficients of high pass mask should be one.

2. Histogram of a digital image with eight quantization level is given below. Perform histogram equalization. Derive the transformation function and the new histogram.

(10)

| Grey level r        | 0  | 1  | 2  | 3   | 4   | 5   | 6   | 7   |

|---------------------|----|----|----|-----|-----|-----|-----|-----|

| Number of pixels nr | 40 | 60 | 80 | 120 | 140 | 160 | 180 | 220 |

3. A digital image with eight quantization levels has the following histogram perform histogram equalization and derive transformation function. Give new equalized histogram.

| Grey level r                                 | 0   | 1   | 2   | 3   | 4  | 5  | 6   | 7   |

|----------------------------------------------|-----|-----|-----|-----|----|----|-----|-----|

| No. of Pixels with grey level n <sub>r</sub> | 120 | 160 | 200 | 150 | 80 | 80 | 100 | 110 |

4. Explain briefly the following operations to digital images along with one application for each : (10)

(i) Median filter. (ii) Image subtraction. (iii) Contrast stretching. (iv) Bit plane slicing. (v) Thresholding.

5. Perform zooming operation using linear interpolation as well as replication, on following image. State which method performs generally better. (4)

| 40 | 60 | 55 | 50 |  |

|----|----|----|----|--|

| 45 | 62 | 48 | 55 |  |

| 20 | 24 | 27 | 34 |  |

| 07 | 06 | 40 | 45 |  |

6. Give following masks of size 3×3 and explain their usefulness in image processing (any four) :

Sobel (ii) Roberts (iii) Low-pass filter (iv) Prewitt

(i) Suppose that a digital image is subjected to histogram equilization. Show that second pass of 7. histogram equilization will produce exactly the same result as first pass.

(10)

(8)

(a) Apply the following Image Enhancement techniques on the given Image. 8.

(10)

(i) Digital Negative (ii) Bit Plane Slicing (iii) Thresholding PVPP'S

College Of Engineering

|   | I | mag | e |   |

|---|---|-----|---|---|

| 2 | 1 | 3   | 4 | 5 |

| 7 | 4 | 2   | 0 | 1 |

| 3 | 5 | 1   | 4 | 6 |

| 0 | 4 | 0   | 2 | 3 |

| 2 | 1 | 6   | 1 | 4 |

**9**. Apply Low Pass and High Pass Spatial Mask on the following image matrix

|                | 5 | 4 | 7 | 1 | 2] |

|----------------|---|---|---|---|----|

| F -            | 6 | 2 | 3 | 4 | 1  |

| $\mathbf{F} =$ | 3 | 5 | 6 | 8 | 2  |

|                | 4 | 3 | 7 | 1 | 8  |

**10**. Apply Low Pass and High Pass Spatial Mask on the following image matrix Prove that Highpass=Original – Lowpass. Assume virtual rows and columns

| 30 | 31  | 32 |

|----|-----|----|

| 33 | 120 | 30 |

| 32 | 32  | 31 |

### 11.

Plot the histogram for the following image. Equalize the histogram and then plot the equalized histogram and the image corresponding to the equalized histogram. The  $4 \times 5$  image is represented by 3 bits/pixel.

| 1 | 3 | 3 | 3 | 2 |

|---|---|---|---|---|

| 3 | 2 | 3 | 1 | 2 |

| 5 | 1 | 1 | 1 | 4 |

| 5 | 6 | 6 | 7 | 0 |

12

DEPARTMENT OF

ELECTRONICS ENGINEERING

**12** Differentiate between point processing and mask processing operations. Classify the following operations into point processing and mask processing operations

- (i) Gray Level slicing

- (ii) Median filtering

- (iii) High pass filtering

- (iv) Edge detection with sobel operator

- (v) Dynamic range compression

- (vi) Thresholding

Draw the transfer characteristics of any two point processing operations.

PVPP'S College Of Engineering DEPARTMENT OF

ELECTRONICS ENGINEERING

### Chapterwise Plan

Subject Title: Digital Signal Processing and Processors

Chapter No. : 2B

Chapter Name : Image Enhancement in Frequency Domain

Approximate Time Needed : 06 hrs

Lesson Schedule :

| Lecture No. | Portion covered per hour                    |

|-------------|---------------------------------------------|

| 11          | 2D -Fourier Transform                       |

| 12          | 2D-DFT                                      |

| 13          | Properties of 2D DFT                        |

| 14          | FFT                                         |

| 15          | LPF, HPF (Ideal, Butterworth, Gaussian)     |

| 16          | High Boost filtering, Homomorphic filtering |

### **Objectives:**

- 1. To yield a better quality image for the purpose of some particular application that can be done by suppressing the noise and improve the image contrast

- 2. To learn Image Enhancement algorithms employed to emphasize, sharpen or smoothen image features in frequency domain for display and analysis.

- 3. To establish a foundation for the fourier Transform and how it is used in basic image filtering

- 4. To implement Fourier transform in the context of Image processing

- 5. Formulation of filtering in the frequency domain.

- 6. Homomorphic filtering

ELECTRONICS ENGINEERING

### **Model Questions:**

- 1. Write short notes on the following :

- (a) Homomorphic filtering.

- (b) Discrete Fourier Transform

- 2. Prove that if an image f(m,n),  $0 \le m \le M-1$  and  $0 \le n \le N-1$  is multiplied by the checkerboard pattern  $(-1)^{m+n}$ . Then its DFT is centered at (M/2,N/2)

- 3. List any two properties of 2D DFT and prove any one of them.

- 4. Explain with block diagram basic steps for filtering in frequency domain.

- 5. What are the steps required to perform filtering in the frequency domain. Also explain the Butterworth Low Pass Filter.

- 6. Explain separability and Translation property of DFT for an image.

- 7. Show that 2D-DFT of an image can be computed by row & column passes with 1D DFT algorithm.

ELECTRONICS ENGINEERING

### <u>Chapterwise Plan</u>

Subject Title: Digital Image Processing

Chapter No. : 3

Chapter Name : Image Segmentation and Image Representation

Approximate Time Needed : 09 hrs

#### Lesson Schedule :

| Lecture No. | Portion covered per hour                     |  |  |

|-------------|----------------------------------------------|--|--|

| 17          | 17 Image Segmentation Based on Discontinuity |  |  |

| 18          | Edge Detection                               |  |  |

| 19          | Hough Transform                              |  |  |

| 20          | Graph – Theoretic Techniques                 |  |  |

| 21          | Thresholding                                 |  |  |

| 22          | Region based Segmentation                    |  |  |

| 23          | Region based Segmentation                    |  |  |

| 24          | Image Representation                         |  |  |

| 25          | Chain Code                                   |  |  |

### **Objectives:**

- 1. Image Segmentation is an essential preliminary step in most automatic pictorial pattern recognition and scene analysis applications.

- 2. To subdivide an image into its constituent regions or objects.

- 3. To extract various features of the image which can be merged or split in order to build objects of interest on which analysis and interpretation can be performed

- 4. To analyze the content of the image and extract important features from image data.

- 5. Learn various thresholding techniques.

- 6. Learn different shape representation techniques

DEPARTMENT OF

College Of Engineering \_\_\_\_\_ ELECTRONICS ENGINEERING

### Chapterwise Plan

Subject Title: Digital Image Processing

Chapter No. : 4

**Chapter Name : Image Compression**

Approximate Time Needed : 12 hrs

### Lesson Schedule :

| Lecture No. | Portion covered per hour                      |  |  |

|-------------|-----------------------------------------------|--|--|

| 26          | Introduction                                  |  |  |

| 27          | Data Redundancy                               |  |  |

| 28          | Image Compression Model                       |  |  |

| 29          | Lossless Compression (Variable Length Coding) |  |  |

| 30          | Lossless Compression (LZW, Bit Plane Coding)  |  |  |

| 31          | Arithmetic Coding                             |  |  |

| 32          | Arithmetic Coding                             |  |  |

| 33          | Fidelity Criteria                             |  |  |

| 34          | Differential PCM                              |  |  |

| 35          | IGS Coding                                    |  |  |

| 36          | Vector quantization                           |  |  |

| 37          | JPEG, MPEG I                                  |  |  |

### **Objectives:**

The student will learn

- 1. Compact Image representation

- 2. To reduce the amount of data required to represent an image

- 3. Techniques to compress amount of data needed to represent information.

- 4. To find statistical properties of the image to design an appropriate compression transformation of the image.

- 5. Image compression standards

### PVPP'S College Of Engineering

DEPARTMENT OF

#### ELECTRONICS ENGINEERING

### Model Questions:

1. State true or false and justify :

(a) Variable length coding procedures can be used to compress a histogram equalized image with 2<sup>n</sup> grey levels.

(b) All image compression techniques are invertible.

- (c) Run length coding always gives data compression.

- (d) Runlength coding is loss-less coding but may not give data compression always.

- (e) In transform based image compression, DCT is widely used as compared to other Transforms.

**2.** (a) Generate Huffman code for the given source. Calculate entropy of the source, average length of the code and the compression ratio achieved :

Symbol

| Symbol      | al   | a2   | a3  | a4  | a5   | a6   | a7   | a8   |

|-------------|------|------|-----|-----|------|------|------|------|

| Probability | 0.06 | 0.02 | 0.3 | 0.5 | 0.04 | 0.01 | 0.03 | 0.04 |

(b) Consider an 8-pixel line grey-scale data, {12, 12, 13, 13, 10, 13, 57, 54}, which has been uniformly quantized with 8-bit accuracy. Construct its 3-bit IGS code. State and explain in brief the type of redundancy which is exploited here to achieve compression.

3. Write short notes on the following :

(a) Fidelity criteria. (b) Transform Coding

4 For a given source  $A = \{a1, a2, a3, a4\}$  the following codes were developed. Check for each of them whether it is uniquely decodable or not. Also state which one is the most optimum compared to others and why? (8)

| Symbols        | Probability | Code 1 | Code 2 | Code 3 |

|----------------|-------------|--------|--------|--------|

| a <sub>1</sub> | 0.5         | 0      | 0      | 0      |

| a <sub>2</sub> | 0.25        | 1      | 10     | 01     |

| a <sub>3</sub> | 0.125       | 00     | 110    | 011    |

| a4             | 0.125       | 11     | 111    | 0111   |

### 5.

- (a) Explain basic data rudendancies. Describe basic compression model used for image 8 compression.

- (b) Classify with reasons, the following data compression techniques into lossy and 8 lossless schemes : (i) Run Length Coding (ii) DCT Compression.

- (c) How many Unique Huffman Codes are there for three symbol source ? Construct 4 these codes.

ELECTRONICS ENGINEERING

### 6.

What are the different types of redundancies that can be present in a digital image **8** and state which method can be used to remove/reduce them ?

- 7. Obtain Huffman Code for the word "COMMITTEE"

- 8. Draw and explain Block diagram of JPEG Encoder & Decoder. (10 marks)

- 9. Mention different steps employed in coding of images using vector quantization

- 10. Encode the statement "I LOVE IMAGE PROCESSING " using the Arithmetic Coding Procedure

PVPP'S College Of Engineering DEPARTMENT OF

ELECTRONICS ENGINEERING

Chapterwise Plan

| Subject T | Title: Digital | Image Pr | ocessing |

|-----------|----------------|----------|----------|

|-----------|----------------|----------|----------|

Chapter No. : 5

Chapter Name : Image Transform

Approximate Time Needed : 08 hrs

### Lesson Schedule :

| Lecture No. | Portion covered per hour    |  |  |

|-------------|-----------------------------|--|--|

| 38          | Matrix Theory               |  |  |

| 39          | Discrete Cosine Transform   |  |  |

| 40          | Discrete Cosine Transform   |  |  |

| 41          | Discrete Hadamard Transform |  |  |

| 42          | Fast Hadamard Transform     |  |  |

| 43          | Fast Hadamard Transform     |  |  |

| 44          | Discrete Wavelet Transform  |  |  |

| 45          | Discrete Wavelet Transform  |  |  |

### **Objectives:**

- 1. To learn Efficient representation of visual information

- 2. Ability to capture significant information of an image in a small description.

- 3. To study 1D and 2D unitary transforms and its properties.

- 4. To gain knowledge of several unitary transforms like DFT, DCT, Hadamard and Wavelet Transform and its implementation on images.

| (            | PVPP'S                                                                                                                                                                                               | DEPARTMENT OF                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 5            | College Of Engineering                                                                                                                                                                               | ELECTRONICS ENGINEERING                             |

|              |                                                                                                                                                                                                      |                                                     |

|              | Model Questions:                                                                                                                                                                                     |                                                     |

|              |                                                                                                                                                                                                      |                                                     |

|              | Explain any two properties of 2-dimensional<br>]t ; find its Hadamard transform.                                                                                                                     | I Fourier transform. (4) If f = [ 1 0 2 3<br>(5)    |

| (a) I        | Explain the property of Hadamard Transform,<br>$f(x) = \{1, 2, 2, 1\}^{f}$                                                                                                                           | also find the Hadamard Transform of 8               |

| (b) T        | hree column vectors are given below :-                                                                                                                                                               | 8                                                   |

| 2002/01/1998 | $\begin{bmatrix} 1 \end{bmatrix} \begin{bmatrix} -2 \end{bmatrix} \begin{bmatrix} 0 \end{bmatrix}$                                                                                                   |                                                     |

|              | $\mathbf{x}_{1} = \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix}, \qquad \mathbf{x}_{2} = \begin{bmatrix} -2 \\ 1 \\ 1 \end{bmatrix}, \qquad \mathbf{x}_{3} = \begin{bmatrix} 0 \\ -1 \\ 1 \end{bmatrix}$ |                                                     |

| sh           | now that they are orthogonal, also generate all P                                                                                                                                                    | ossible Pattern.                                    |

|              | xplain the following Property of Image Transfo                                                                                                                                                       | rm 4                                                |

| (i           | ) Symmetrical (ii) Orthonormal.                                                                                                                                                                      |                                                     |

| 1.           | Compute DFT and DCT of the following                                                                                                                                                                 | Image                                               |

|              | 1 3 4 5                                                                                                                                                                                              |                                                     |

|              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                |                                                     |

|              | 5 4 3 1                                                                                                                                                                                              |                                                     |

| 2.           | Show that 2D-DCT can be computed by r                                                                                                                                                                | ow and column passes with 1D-DCT algorithm          |

| 3.           |                                                                                                                                                                                                      |                                                     |

| 4.           | For 2x2 transform A and the image U, Co<br>$A = \frac{1}{\sqrt{2}} \begin{bmatrix} 1 & 1 \\ 1 & 1 \end{bmatrix},  U = \begin{bmatrix} 1 & 2 \\ 3 & 4 \end{bmatrix}$                                  | mpute Transformed image V and the basis image       |

|              | $\sqrt{2} \begin{bmatrix} 1 \\ 1 \end{bmatrix}^{\prime} = \begin{bmatrix} 3 \\ 4 \end{bmatrix}$                                                                                                      |                                                     |

| 5.           | Justify/ Contradict the following Stateme                                                                                                                                                            | nte                                                 |

| 5.           |                                                                                                                                                                                                      | arable and symmetric, the transform can be expresse |

|              | in matrix form.                                                                                                                                                                                      |                                                     |

|              | b. Walsh Transform is nothing but sequ                                                                                                                                                               | ency ordered Hadamard matrix                        |

|              |                                                                                                                                                                                                      |                                                     |

|              |                                                                                                                                                                                                      |                                                     |

|              |                                                                                                                                                                                                      |                                                     |

|    | PVPP'S                                                                                                                    | DEPARTMENT OF                                  |

|----|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|    | College Of Engineering                                                                                                    | ELECTRONICS ENGINEERING                        |

| 6. | Let $A = \begin{bmatrix} 1 & 1 \\ 1 & 1 \end{bmatrix}$ , $B = \begin{bmatrix} 1 & 2 \\ 3 & 4 \end{bmatrix}$ . Find Kroned |                                                |

|    | your result.                                                                                                              |                                                |

| 7. | Write the expression of DFT. State and expla                                                                              | ain the properties of 2D-DFT.                  |

| 8. | Write short note on 2D wavelet Transform I                                                                                | Filter Bank.                                   |

| 9. | <b>č</b>                                                                                                                  | forward and inverse transforms and compare the |

|    | inverse transform with the digitized image. $\begin{bmatrix} 2 \\ 1 \\ 1 \\ 2 \end{bmatrix}$                              | 0 1 0<br>1 0 1<br>0 0 1<br>1 2 3               |

|    | (i) DFT (ii) DCT                                                                                                          |                                                |

|    | ., .,                                                                                                                     |                                                |

PVPP'S College Of Engineering DEPARTMENT OF

ELECTRONICS ENGINEERING

Chapterwise Plan

Subject Title: Digital Image Processing

Chapter No. : 6

Chapter Name : Binary Image Processing

Approximate Time Needed : 07 hrs

### Lesson Schedule :

| Lecture No. | Portion covered per hour                    |  |  |  |  |

|-------------|---------------------------------------------|--|--|--|--|

| 46          | Binary Morphological Operators              |  |  |  |  |

| 47          | Hit-or-Miss Transformation,                 |  |  |  |  |

| 48          | Boundary Extraction, Region Filling         |  |  |  |  |

| 49          | Thinning and Thickening                     |  |  |  |  |

| 50          | Connected Component Labeling                |  |  |  |  |

| 51          | Iterative Algorithm and Classical Algorithm |  |  |  |  |

| 52          | Iterative Algorithm and Classical Algorithm |  |  |  |  |

### **Objectives:**

This chapter gives overview of different operations involved in Binary Image Processing. The objective is to make the students familiar with the following concepts

- 1. Basic idea of mathematical morphology

- 2. Binary morphological operations like thinning, thickening, hit or miss transform etc.

ELECTRONICS ENGINEERING

### **Model Questions:**

- 1. Explain the following operations

- **1**. Erosion

- **2.** Dilation

- **3.** Closing

- **4**. Opening

- 2. Explain HIT or MISS Transformation

- 3. Explain the importance of boundary extraction. Generate an algorithm to perform the same.

- 4. Explain the following transformation in detail

- **1**. Thinning

- **2.** Thickening

- **3.** Skeletonization

- **4.** Pruning

DEPARTMENT OF

College Of Engineering \_\_\_\_\_ ELECTRONICS ENGINEERING

### **ASSIGNMENT (CASE STUDY)**

DATE OF SUBMISSION : 30th September 2015

| Group     | Case Study                                          |

|-----------|-----------------------------------------------------|

| No.       |                                                     |

| E1        | Digital Watermarking                                |

| E2        | Face Recognition                                    |

| E3        | Finger print Recognition                            |

| E4        | Signature Recognition                               |

| E5        | Vehicle number plate detection and recognition      |

| <b>E6</b> | Object Detection using Correlation principle        |

| E7        | Person Tracking using DWT                           |

| <b>E8</b> | Handwritten Character recognition                   |

| E9        | Printed Character Recognition                       |

| E10       | Content based image retrieval                       |

| E11       | Text Compression                                    |

| E12       | Image Compression Standards                         |

| E13       | Image processing techniques for mobile applications |

| E14       | Image Acquisition                                   |

| E15       | Satellite Images                                    |

| E16       | Change Detection                                    |

| E17       | Thresholding                                        |

| E18       | Adaptive Thresholding                               |

| E19       | Medical Image Processing                            |

| E20       | Satellite Image Processing                          |

### FORMAT FOR CASE STUDY

Abstract : Introduction : Literature Survey : Conclusion :

DEPARTMENT OF **PVPP'S** ELECTRONICS ENGINEERING College Of Engineering B. E. ETRX VII (R) 21515 DIPD **QP Code : 8469** Maximum marks 100 **Duration 3 Hours** Instructions : 1. Question No.1 is compulsory. 2. Out of the remaining questions attempt any four. 3. Figures in the bracket indicate maximum marks. Q 1. Answer the following: a) What do you mean by zero memory operations? [05] b) Differentiate between 8 connectivity and m connectivity. [05] [05] c) What is truncated Huffman code? d) Justify the statement: " Laplacian filter is a high pass filter." [25] Q.2. Explain the following enhancement operations and draw the graph of transformation [10] a) function: i) Dynamic range compression ii) Gray level slicing Perform histogram equalization on the following image histogram and plot original and [10] b) equalized histograms.

Gray Level

0

1

2

3

4

5

6

7

Number of pixels

550

300

0

0

0

200

325

225

03. [10] Explain in detail the types of data redundancies seen in digital images a) b) Explain the method of edge linking using Hough Transform. [10] Q4. a) Calculate the 2DDFT and Hadamard transform of the image segment shown below using [08] matrix multiplication method. 0014 1114 f(x,y) =1010 0202 Explain the importance of kernel separability property of 2DDFT in implementing 2DFFT. [06] b) [06] Differentiate between spatial and tonal resolution. c) Q 5. [10] Explain why it is difficult to threshold images with poor illumination. a) With the help of a neat block diagram, explain the working of a homomorphic filter. [10] b) Q 6. What are Fourier Descriptors? Explain how a two dimensional boundary is represented [10] a) using Fourier Descriptors. [10] Explain how Huffmian code removes coding redundancy. b) [20] Q 7. Write short notes on any four of the following: b) Wavelet transform a) Moments d) Biometric authentication c) Digital water marking Motion based segmentation e)

RJ-Con. 10025-15.

31

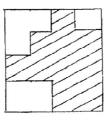

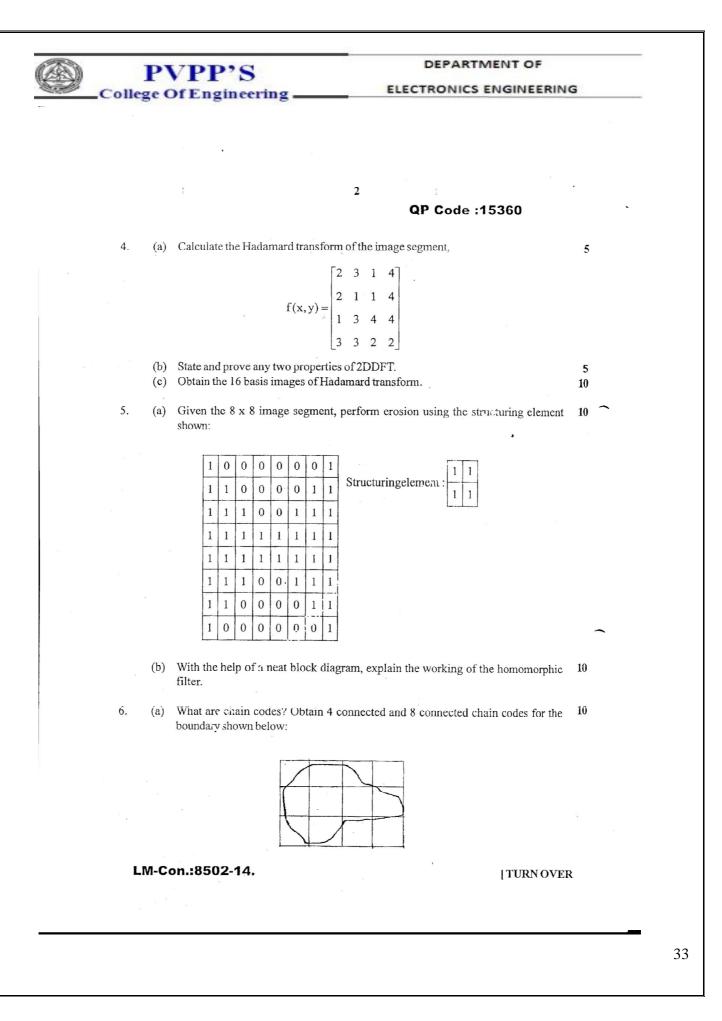

DEPARTMENT OF PVPP'S ELECTRONICS ENGINEERING College Of Engineering Elective I Election 1 27/11/2014 Digital I make Processing by stem BE Sem VII QP Code :15360 | Total Marks : 100 (3 Hours) N.B: (1) Question No. 1 is compulsory. (2) Out of the remaining questions attempt any four. (3) Figures in the right indicate maximum marks. Answer any four : 1. (a) Differentiate between spatial and tonal resolutions. 5 5 (b) Why is the sum of coefficients of a high pass filter mask zero? 5 (c) Compare Huffman coding and arithmetic coding; (d) Give 3x3 masks for Laplacian filter, horizontal, vertical,  $+45^{\circ}$  and  $-45^{\circ}$  line 5 detectors. 5 (e) Explain dilation and erosion in brief. 10 2. (a) Explain the following enhancement operations and draw the graph of transformation function : (i) Clipping, (ii) Bit plain slicing 10 (b) Perform histogram equalization on the following image histogram and plot original and equalized histograms. **Gray Level** 0 1 4 5 7 2 6 200 300 500 350 0 0 Number of pixels 250 0 3. (a) A source emits 6 symbols with the following probabilities : 10 Symbol В D Е F A C Probability 0.1 0.2 0.05 0.05 0.35 0.25 Construct the Huffman code. Calculate the average code word length and coding efficiency. (b) Perform region splitting and merging on the image segment shown below. Draw the 10 quad tree. Briefly explain the method used.

LM-Con.:8502-14.

[TURN OVER

32

| Ð | PVPP'S<br>College Of Engineering                                                                                                                                                                                                                   | DEPARTMENT OF<br>ELECTRONICS ENGINEERING           |    |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----|--|

|   |                                                                                                                                                                                                                                                    | 3<br>QP Code :15360                                |    |  |

|   |                                                                                                                                                                                                                                                    | f data redundancies present in the digital images. | 10 |  |

|   | <ul> <li>7. Write short notes on any four of the fol</li> <li>(a) Opening and closing</li> <li>(b) Color models</li> <li>(c) Finger print recognition</li> <li>(d) Digital water marking</li> <li>(e) Handwritten character recognition</li> </ul> |                                                    | 20 |  |

|   |                                                                                                                                                                                                                                                    | · · · · · · · · · · · · · · · · · · ·              |    |  |

| ~ |                                                                                                                                                                                                                                                    | ,                                                  |    |  |

|   | LM-Con.:8502-14.                                                                                                                                                                                                                                   |                                                    |    |  |

| PVPP'S     College Of Engineering                                                             |                                                                                                                                                           |                                                                                      |                                                                                          |                                                                                   | DEPARTMENT OF<br>ELECTRONICS ENGINEERING                 |                                              |                                 |                   |                              |         |         |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|---------------------------------|-------------------|------------------------------|---------|---------|

|                                                                                               |                                                                                                                                                           |                                                                                      |                                                                                          |                                                                                   |                                                          |                                              |                                 |                   |                              |         |         |

| 14-11-13-DTP<br>Con. 848                                                                      |                                                                                                                                                           | c                                                                                    | ftei S                                                                                   | ed J<br>Sem                                                                       | Ma                                                       | ge<br>P E                                    | Proce<br>7 RX                   | oning<br><b>J</b> | ) گوين<br>ه/۱/۱ع<br>LJ-1399( | р.<br>1 |         |